TimeWeaver

Multi-core timing analysis for complex parallel systems

TimeWeaver combines static analysis with non-intrusive measurements to provide worst-case execution time estimates.

Multi-Core Timing Challenges

Modern embedded systems increasingly use multi-core processors. TimeWeaver addresses the complex timing analysis challenges that arise from parallel execution, shared resources, and inter-core interference.

Interference Analysis

Model and analyze interference between cores sharing resources

Cache Coherency

Account for cache coherency protocols in timing analysis

Precise Bounds

Provide tight and safe WCET bounds for multi-core systems

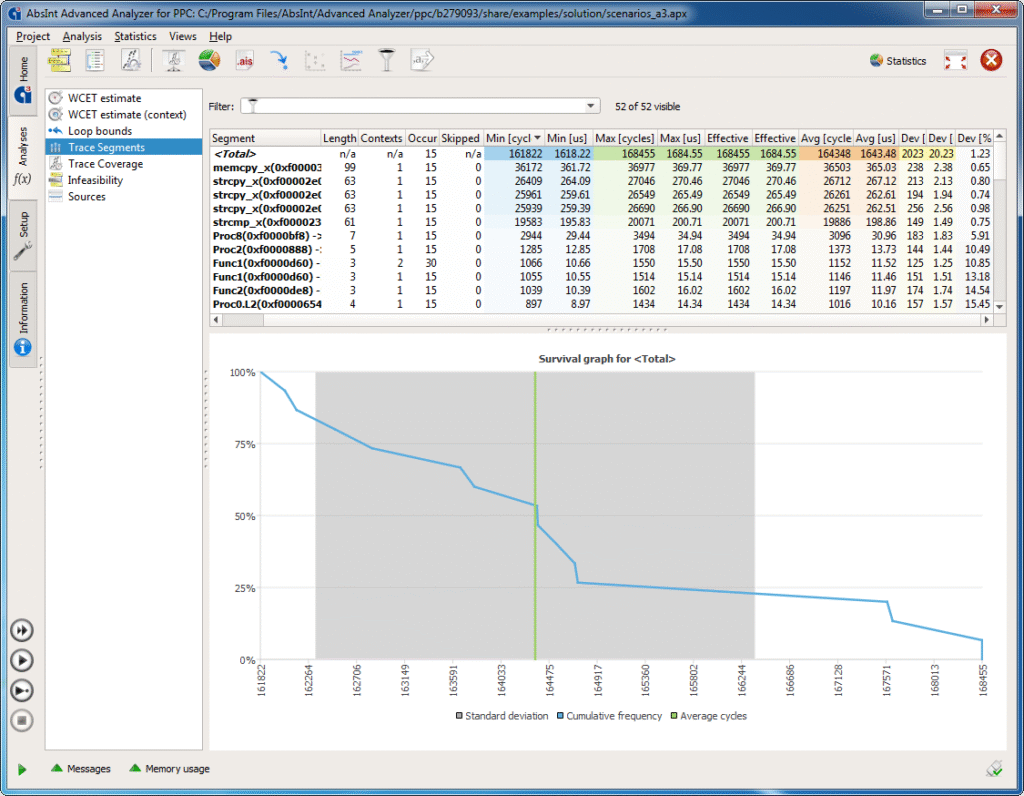

Survival graph

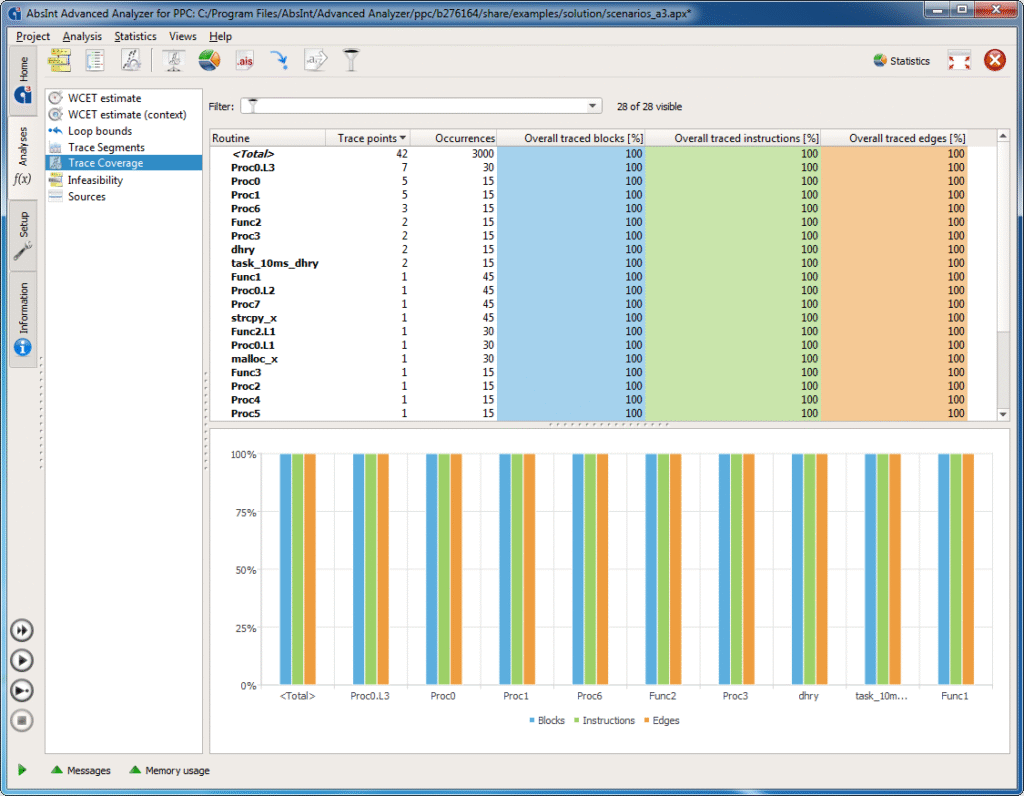

Coverage analysis

The tool estimates the worst-case execution time (WCET) of tasks based on the execution time of trace segments obtained from real-time instruction-level tracing. The computed time bounds are valuable for soft real-time systems and provide feedback for optimizing worst-case performance.

Your Benefits

- The hybrid approach works for a wide range of modern high-performance processors that are not statically predictable anymore, not even by a most sophisticated tool such as aiT. This includes multi-core processors where inter-core interferences cannot be prevented or controlled in a satisfactory way, or where the available documentation is insufficient to build a static timing model.

- TimeWeaver is non-intrusive. It needs no code instrumentation that distorts timing measurements. It uses the embedded trace units of modern embedded processors (Nexus 5001, CoreSight ETM, etc.) to observe program flow. Interference effects included in the traces, such as access delays to shared resources, are taken into account. This approach is compliant with the recommendations of CAST (CAST-32A) and EASA (AMC 20-193).

Workflow

TimeWeaver takes as input:

- 1. a binary executable

- 2. execution traces, e.g. BHM traces compliant to the IEEE-ISTO 5001 standard

- 3. optional user annotations, e.g. on loop bounds, in the same format as other AbsInt analyzers such as aiT or StackAnalyzer

TimeWeaver then provides a safe upper bound of the length of the longest execution path, based on the local time measurements in the traces.

Features

The analysis results reported by TimeWeaver include:

- global end-to-end time, based on the maximum observed trace segment times combined to an overall bound

- end-to-end bounds for specific functions, depending on trace points

- coverage of the control-flow graph by the input traces

- maximum possible and maximum observed iteration counts for loops

- time variance of each code segment over all traces

TimeWeaver offers the same powerful user interface you are used to from working with other AbsInt tools, with fully integrated graphical and textual viewers for control flow, analysis results, source code, assembly code, and configuration files. You can:

- interactively explore analysis results

- save, restore, and compare analysis scenarios

- export customizable reports for documentation and certification purposes

- start all analyses from the same GUI and handle all the tools with the same look and feel

Qualification support

Your usage of TimeWeaver can be qualified according to ISO 26262, DO-178B/C, and other safety standards. We offer special Qualification Support Kits that help you simplify and automate your qualification process.

Advanced Capabilities

- Multi-core timing analysis

- Cache coherency modeling

- Interference analysis

- Parallel execution modeling

- Scalable architecture support

Analysis Process

1.System Modeling

Model the multi-core architecture and shared resources

2.Interference Analysis

Analyze interference patterns between cores

3.WCET Computation

Calculate worst-case execution times considering all factors

Target Multi-Core Systems

Automotive ECUs

Multi-core automotive control units

- ADAS systems

- Engine management

- Infotainment

Aerospace Systems

Critical avionics applications

- Flight control

- Navigation

- Communication

Industrial Control

Complex control systems

- Process control

- Robotics

- Factory automation

Master Multi-Core Timing

Unlock the potential of multi-core systems with precise timing analysis